### Bridging among Chip, Package And System in the Industry

Youngsoo Lee

Senior Product Manager, CPS Solutions

ANSYS

ONVERGENCE 参 2017 ANSYS用户技术大会

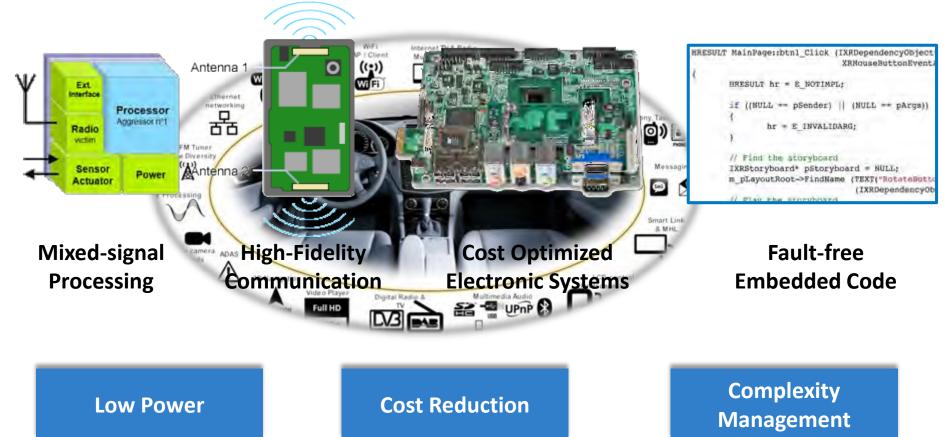

#### **Electronic System Design Challenges**

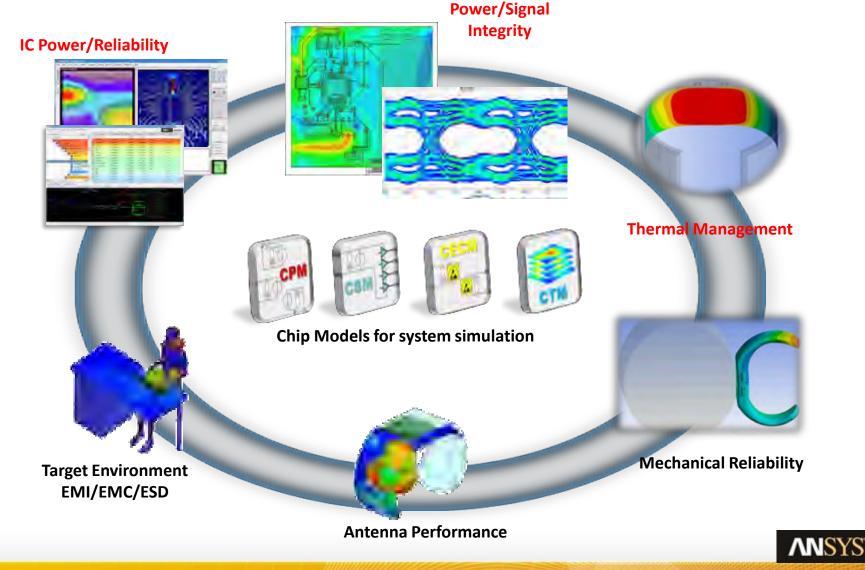

#### Single-Platform Multiphysics and Multiscale Design Exploration Encompassing Entire Electronic System is Necessary

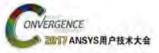

#### Industry Reality: Separated due to Conventional Env. & Silo

- Essential elements crucial to performance should be decided by co-design

- Separated chip, package and board development owner and process

- Insufficient information/interest about other parts due to silo

- No integrated team and design methodology encompassing all parts

- Different knowledge scope : alien to each other

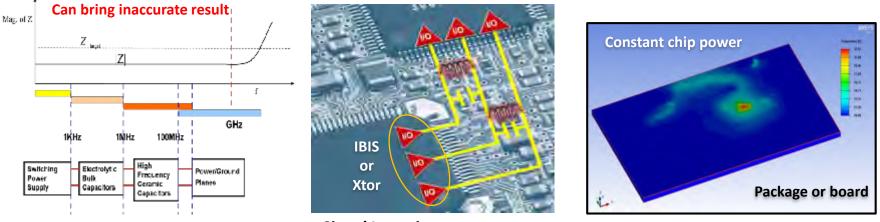

#### **Traditional Power/Signal/Thermal Performance Check**

System Level: Individual part is designed with its own target spec

Power Integrity

Signal Integrity

**Thermal Integrity**

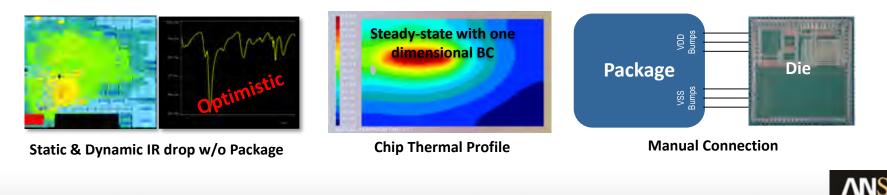

Chip Level: Chip only or lumped model, Manual Connection

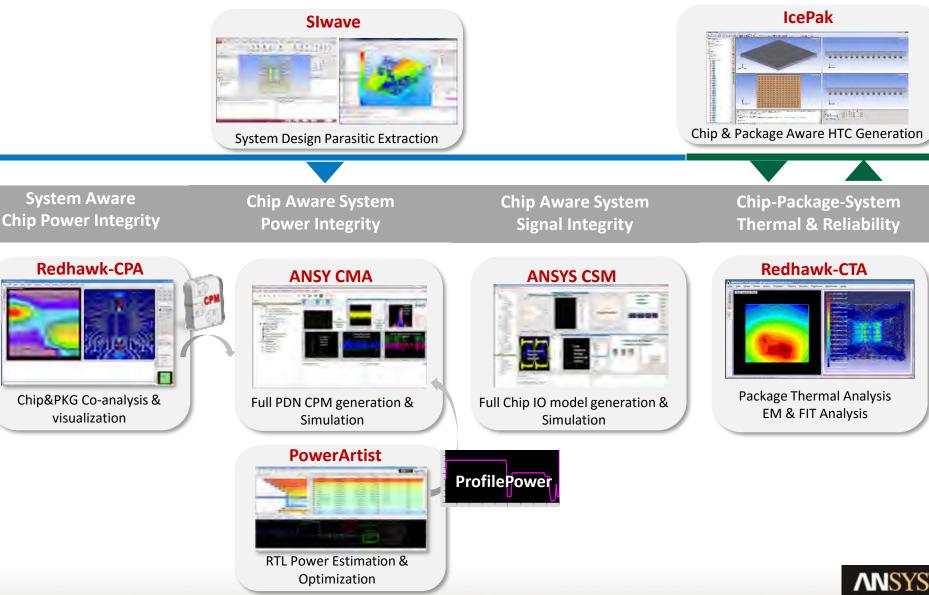

#### ANSYS Chip Package System Convergence Power, Thermal, Reliability, EMI and SI

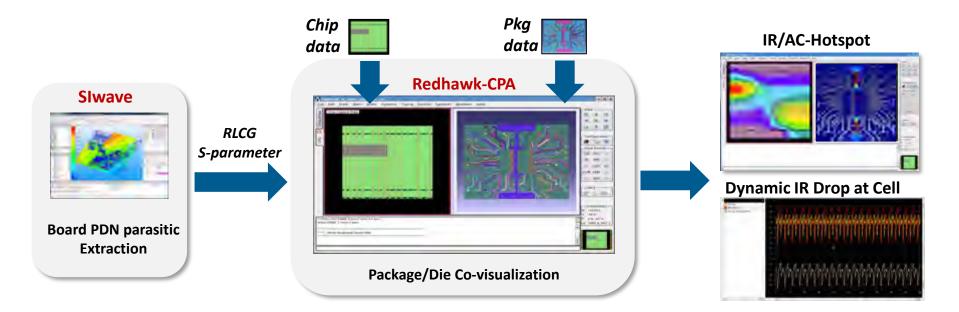

#### System Aware Chip Level Power Integrity Analysis

- Involved ANSYS products: SIwave, Redhawk/Totem-CPA

- Chip-Aware Package AC/DC hotspot => Optimization

- Board & Package aware IR/DvD

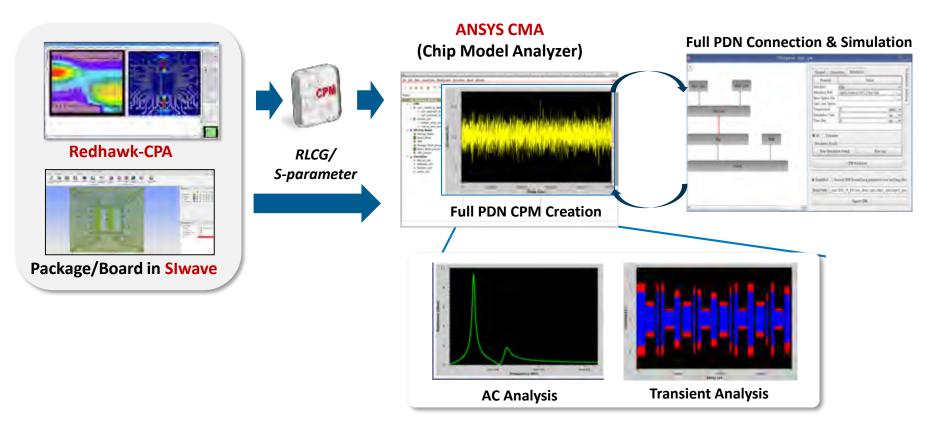

#### **Chip Aware System Level Power Integrity Analysis**

- Involved ANSYS productions: SIwave, Redhawk/Totem-CPA, ANSYS CMA

- Generates full PDN coverage current model

- Full PDN performance check through AC & transient simulation

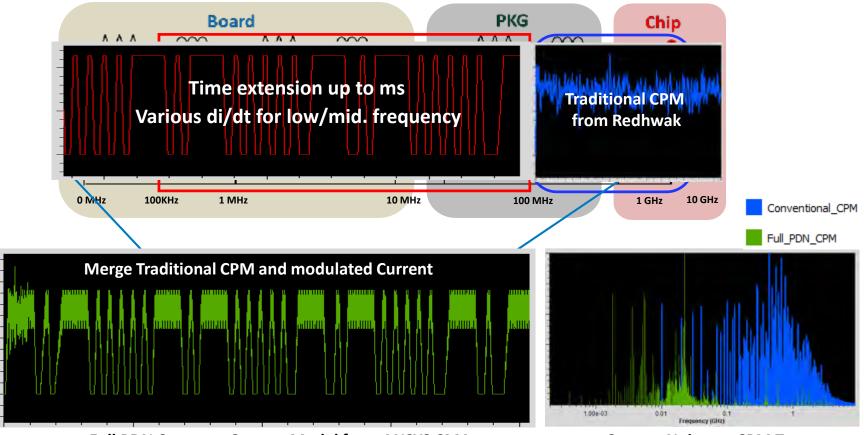

#### **Accurate Current Model for Full PDN Analysis**

Full PDN Coverage Current Model from ANSYS CMA

**Current Noise vs. CPM Types**

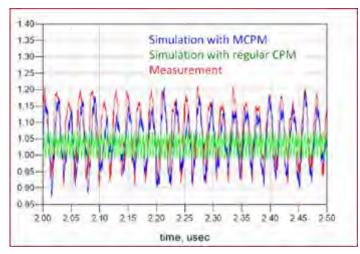

#### System Level PI Analysis Case Study : CISCO & ST

Power Noise Detection & Mitigation with Full PDN Coverage CPM

Correlation Comparison vs. CPM types

| Configurations | Description                                                                     | Simulated<br>noise<br>[mV] | Measured<br>noise<br>[mV] |

|----------------|---------------------------------------------------------------------------------|----------------------------|---------------------------|

| Test case 1    | Baseline                                                                        | 384                        | 356                       |

| Test case 2    | Chip with additional 50% ODC                                                    | 272                        | 259                       |

| Test case 3    | Chip with additional<br>50% ODC + Package<br>cap count increased<br>from 2 to 6 | 217                        | 222                       |

Voltage Drop Mitigation based on Full PDN Coverage CPM

- Voltage drop(50mV) with regular CPM brings very optimistic result

- Only full PDN coverage CPM(=MCPM) detects severe power noise

- PDN can be only optimized by power noise analysis with full PDN CPM

\* Sourced by Di Hu, Yongxue Yu, Antonio Ferrario, Olivier Bayet, "System Power Noise Analysis Using Modulated CPM", IEEE 2015

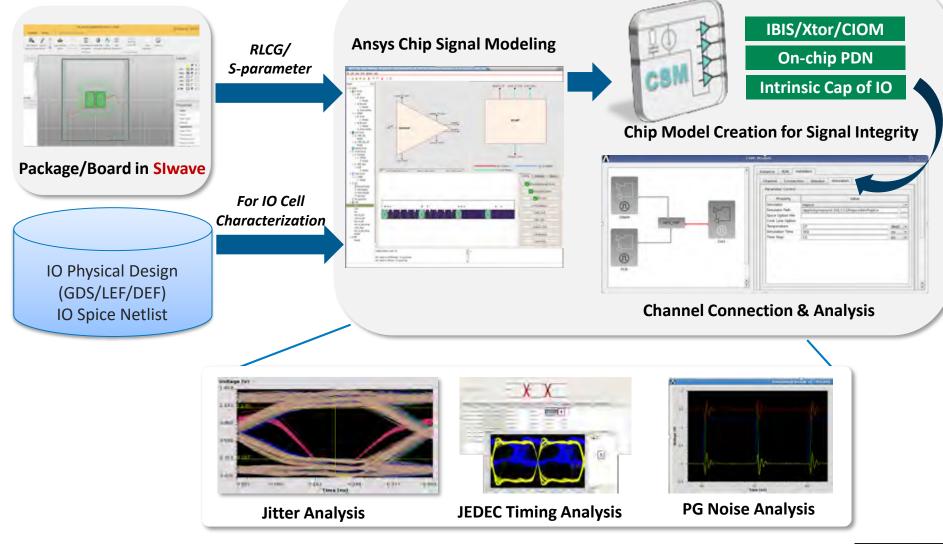

Chip Aware System Level Signal Integrity Analysis

**ANSYS**

#### Accurate & Fast Chip Model for Signal Integrity

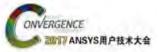

#### IBIS vs. Xtor vs. CSM

Measurement correlated

July 31, 2017

# System Level SI Analysis Case Study

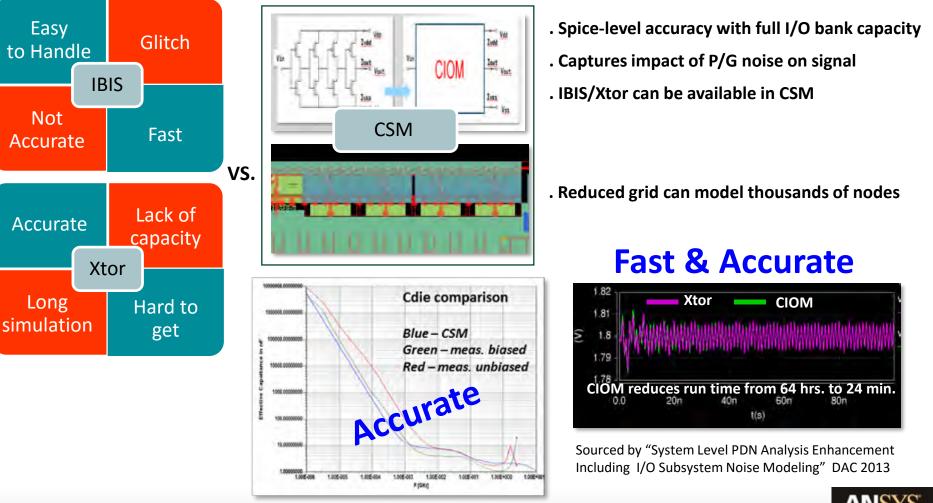

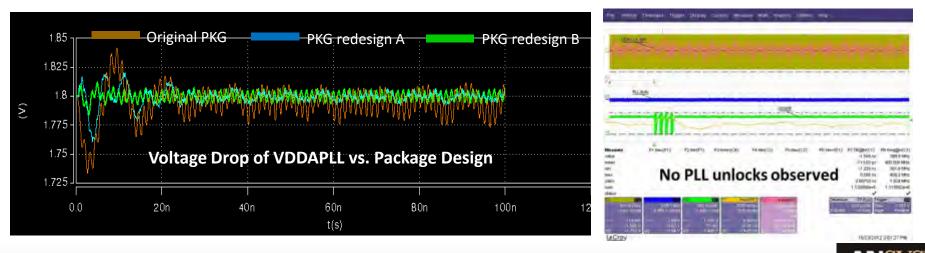

Root Causing of PLL Failure and Guide Redesign of Chip-Package Routing

Noise from DDR signal(B5) activity on PLL PG supply(VDDAPLL) results in PLL Failure(unlock)

Original Package

PKG redesign A: reducing impedance and ground bounce by merging PLL\_VSSA to chip VSS PKG redesign B: reducing impedance by shorting VDDAPLL with IO Power(VDDA1.8)

Sourced by "System Level PDN Analysis Enhancement Including I/O Subsystem Noise Modeling" DAC 2013

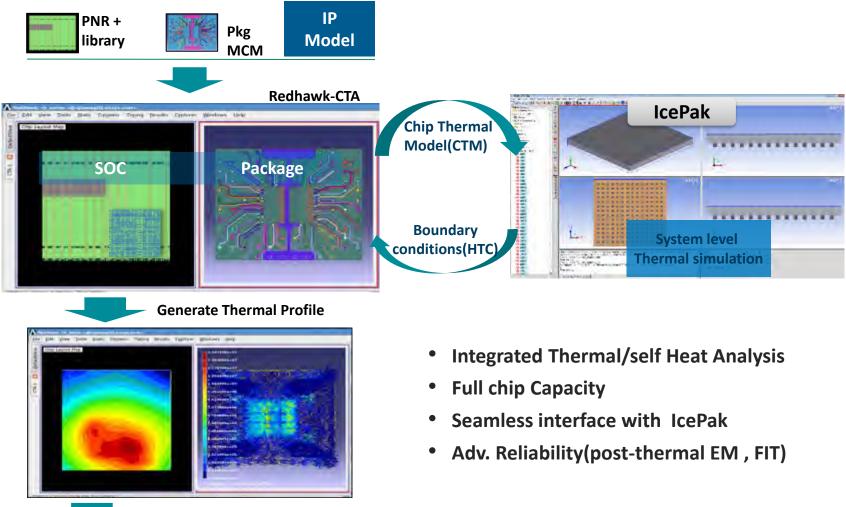

#### Chip-Package-System Thermal Aware Reliability Analysis

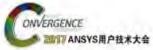

### **Case Study: Thermal-aware EM for Analog IP**

#### Thermal aware EM sign-off is a must for FinFET designs

Source: "A Thermal-aware Electromigration and Failure-in-Time Reliability Flow", Xilinx Inc., DAC 2017

14 © 2017 ANSYS, Inc. July 31, 2017

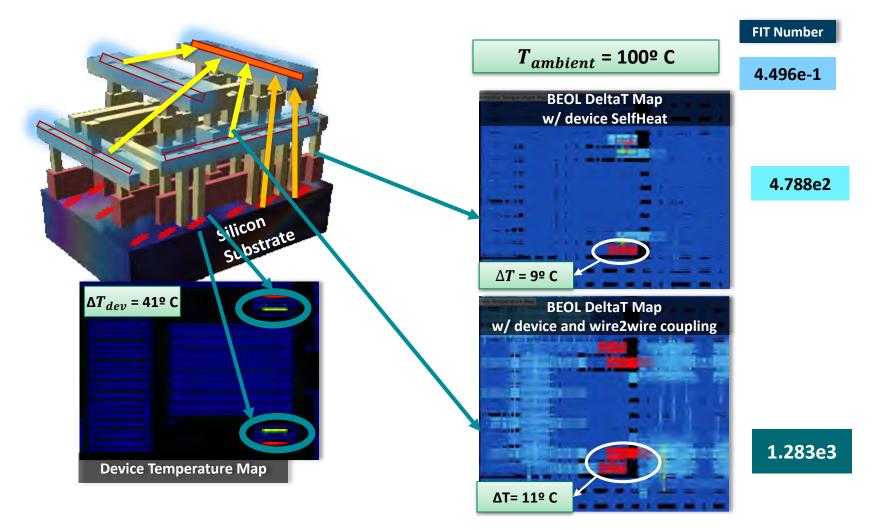

#### **Case Study: Thermal-aware Statistical EM for SoC**

"Thermal-aware SEB for Advanced FinFET EM Sign-off", Hisilicon Technologies, DAC 2017

#### **ANSYS Chip Package System Power/Signal/Thermal Integrity**

16 © 2017 ANSYS, Inc.

July 31, 2017

## 感谢聆听