## **Ensuring ESD Robustness for IPs and SoCs**

DanYu / CAD support engineer

Analogix

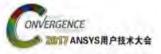

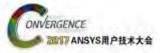

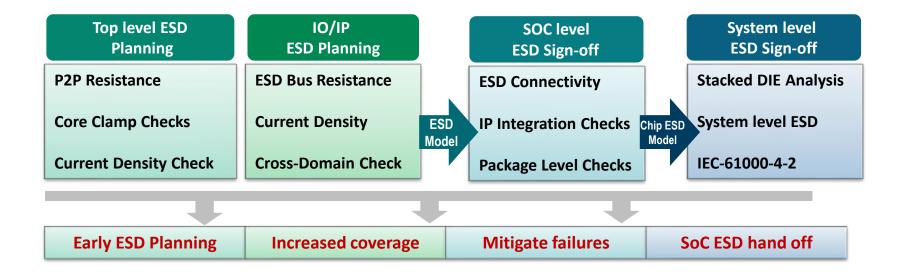

## **Challenges in ESD Design**

Higher Integration

#### Thinner oxides Thinner Interconnects Smaller devices

Power/Ground islands Unique ESD requirements Higher pin-counts

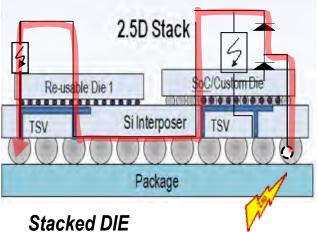

#### Evolving Technologies

Stacked DIE HBM, Memory Cube System in Package

Systematic ESD verification is a must to ensure first silicon success

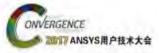

## **ANSYS** PathFinder<sup>™</sup>: SoC and IP ESD Integrity

## Analogix use pathfinder for ESD sign-off

#### **ESD connectivity check**

**VSYS**用户技术大:

- Do we have unconnected Clamp Instance ?

- Do we have bumps isolated from Clamps ?

- Do we have proper stage of ESD connectivity for each net-pair ?

#### **Rule based Resistance check**

• Is our ESD path's resistance small enough to protect function circuit ?

#### **Rule based Current Density check**

• Is our ESD path's routing strong enough to bear big ESD discharge current ?

#### Analog case overview

| Process      | TSMC 28HPC+                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Size         | 6350umx4770um                                                                                                  |

| No. of Bumps | <ul> <li>259 Bumps         <ul> <li>-14 Power</li> <li>- 16 Ground</li> <li>- 65 Signal</li> </ul> </li> </ul> |

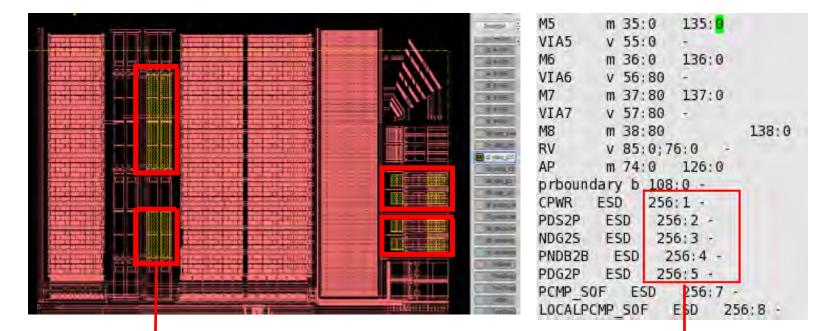

## How to recognize ESD cell?

• Drawing corresponding GDS mark layer on ESD cell ( clamp/diode )

Mark layer can be used for Both the ESD and device identification purposes in GDS2DB

Define different layer number in GDS layermap to identify different ESD cells

## How to model ESD cell?

#### 1. Use R-ON/R-OFF model to define each type of ESD cell

```

BEGIN CLAMP CELL

BEGIN CLAMP TYPE

NAME <cell name>

CLAMP TYPE PCMP SOF

TYPE <user type name>

CELL NAME anx maple chip PCMP SOF *

? PIN [<pin name> | NA] [<x loc> <y loc>]

PIN TYPE pwr AVDD10 ck AVDD10 data AVDD18 PAD AVD

[ BOTTOM | TOP |<layername>] <locID> ?

1V01 PAD DVDD1V23 PAD DVDD PLL PAD PVIN PAD SVIN

? XTOR <xtorName>:<net> <x loc> <y loc> <layer> <locID> ?

PIN TYPE gnd AVSS10 ck AVSS10 data AVSS18 PLL AVS

AVSSIO PAD AVSS VCO DVSS1V01 PAD DVSS1V23 PAD DVS

? RON <clamp On Resistance Ohms> ?

BEGIN PIN TYPE

? ESD PIN PAIR <loc ID1> <loc ID2> [

NAME pwr

[ <Ron> | [ <Ron+>|OFF] [<Ron->|OFF] ]?

SHORT 1

<I-V clamp name> ]?

END PIN TYPE

? IMAX <I1> [<I2>] ?

BEGIN PIN TYPE

? VMAX <V1> [<V2>] ?

NAME gnd

? RAIL VOLTAGE <voltage> ?

SHORT 1

END CLAMP CELL

END PIN TYPE

PIN PAIR pwr and 0.1 off

END CLAMP TYPE

Resistance value is 0.1\Omega when clamp is

on,When current from gnd to pwr, clamp is off

```

# Defines legal ESD discharge path and resistance values for both current discharge directions

7

#### How to model ESD cell?

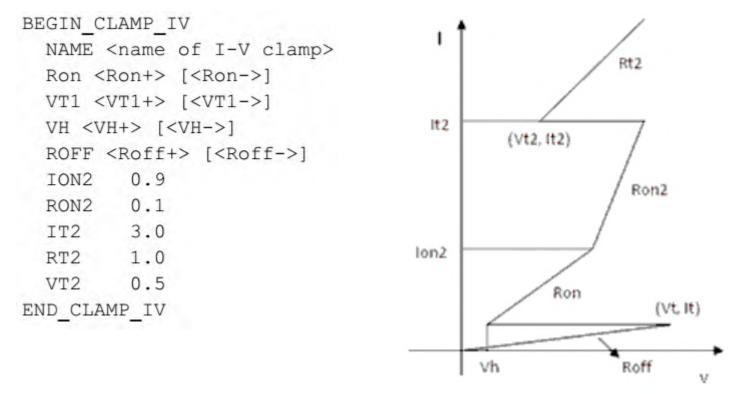

#### 2. Use IV-Curve to define each type of ESD cell

All clamp cells are modeled as resistors with IV curve

#### **ESD Connectivity and Rule Checks**

- Full SoC Capacity

- Multi-threaded solve

- Simple and customizable rules

- Isolated Bumps/Clamps Checks

- Pin2 Pin ESD Connectivity Checks

- Pin2Pin Resistance Checks

- Layout-based Debug

## **ESD Connectivity Check**

• List of Bumps Isolated from Clamps

| ######### List of Bumps :<br>#                | solated                          | from Cla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | amps ###                                    | #######    |

|-----------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|

| # <bump_name> <bump_x> ·</bump_x></bump_name> | <bump_y></bump_y>                | <bump_l <="" td=""><td>AYER&gt; <ne< td=""><td>ET_NAME&gt;</td></ne<></td></bump_l>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AYER> <ne< td=""><td>ET_NAME&gt;</td></ne<> | ET_NAME>   |

| AVDD18_PAD_Def 2786.24                        | -10.07                           | AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AVDD18_                                     | PAD        |

| AVDD18_PAD.extra1_Def                         | 1881.84                          | 3.515                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AP                                          | AVDD18_PAD |

| PAD PVIN Def 5993,11                          | 4431.71                          | AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PAD PVI                                     | V          |

| PAD PVIN.extral Def                           | 5993.11                          | 4246.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AP                                          | PAD PVIN   |

| PAD PVIN.extra2 Def                           | 5993,11                          | 4340.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AP                                          | PAD PVIN   |

| PAD PVIN.extra3 Def                           | 6060.52                          | 4340.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AP                                          | PAD PVIN   |

| PAD PVIN.extra4 Def                           | 6060.52                          | 4246.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AP                                          | PAD PVIN   |

| PAD_PVIN.extra5_Def                           | the loss was been and the second | and the second se |                                             | PAD_PVIN   |

Bumps doesn't have connections to clamp cell will be reported as shown, includes bump name/location/layer /net name

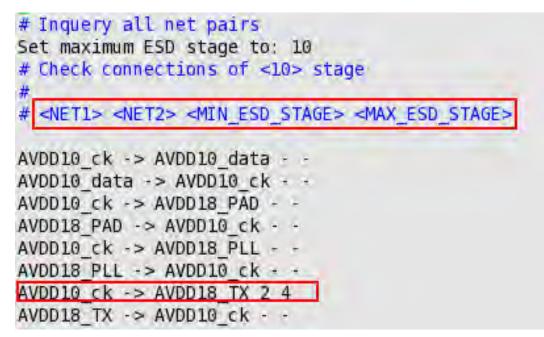

### **ESD Connectivity Check**

• Net-Pair ESD connectivity

Reports the min/max ESD stage between ESD net pair Minimum 2 stages and up to 4 stages ESD connection between AVDD10\_CK and AVDD18\_TX as shown

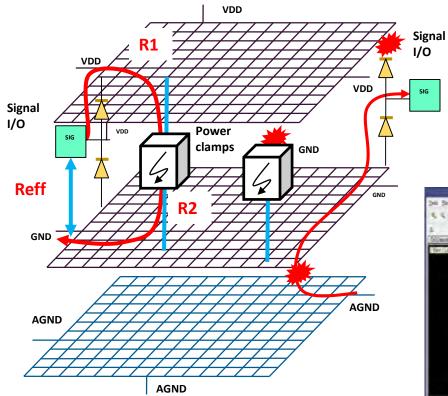

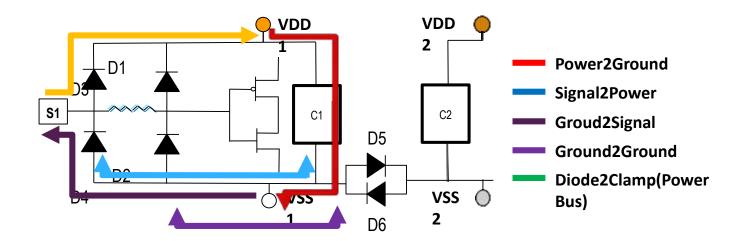

### Rule Based RES Check

**Resistance check rule :**

- 1. B2B (Power pad to Ground pad) < 1 Ohm

- 2. B2B (Signal pad to Power pad) < 1 Ohm

- 3. B2B (Ground pad to Signal pad) < 1 Ohm

- 4. B2B (Ground1 pad to Ground2 pad) < 1 Ohm

- 5. C2C (Diode to Clamp) < 1 Ohm

#### Analogix R Check Case

|                                   | B2BM pad_r_sw_Def -> AVDD18_PLL_Def ( 1-1 ) |                     |        |          |         | 00       |          |

|-----------------------------------|---------------------------------------------|---------------------|--------|----------|---------|----------|----------|

| Clamp(M1)                         |                                             | Point               | Layer  | Res(Ohm) | ResDiff | Volt(mV) | VoltDiff |

|                                   | 1                                           | (1129.095, 4391.6   | н M1   | 11.687   | -       | 0.000    |          |

|                                   | 2                                           | (1131.465,4381.6    | M1     | 11.687   | 0.000   | 0.000    | 0.000    |

|                                   | 3                                           | ( 1131.465 , 4371.9 | M1     | 9.560    | 2.127   | 98.013   | -98.013  |

|                                   | 4                                           | ( 1130.815 . 4370.2 | M1     | 6.082    | 3.478   | 113.529  | -15,516  |

|                                   | 5                                           | (1130.815, 4370.2   | M2     | 5.734    | 0.348   | 115.647  | -2.119   |

|                                   | 6                                           | ( 1130.815 , 4370.2 | M3:    | 5.386    | 0.348   | 120,117  | -4.470   |

|                                   | 7                                           | ( 1130.815 , 4370.2 | - M4   | 4.853    | 0.533   | 129.796  | 9.679    |

|                                   | 8                                           | (1130.815, 4370.2   | M5     | 4.320    | 0.533   | 139.298  | -9.502   |

|                                   | 9                                           | (1130.815, 4370.2   | M6     | 3.786    | 0.533   | 149,122  | -9.824   |

|                                   | 10                                          | ( 1130.905 . 4370.2 | . M6   | 3.776    | 0.010   | 149,592  | -0.470   |

|                                   | 11                                          | (1130.905, 4370.2   | M7     | 3.726    | 0.050   | 154.668  | -5.076   |

|                                   | 12                                          | ( 1129.785 , 4370.2 | M7     | 3.720    | 0.006   | 155.084  | -0.416   |

| Bump(AP)                          | 13                                          | ( 1126.690 , 4369.1 | M8     | 3.711    | 0.008   | 161,984  | -6 900   |

| x1                                | 14                                          | ( 1126.690 , 4337.6 | PM 149 | 3.627    | 0.084   | 223.608  | -61.624  |

|                                   | 15                                          | ( 980.110 , 4337.66 | ST MB  | 3.117    | 0.509   | 767.446  | -543.838 |

|                                   | 16                                          | ( 980.110 , 4334.66 | 5.) M8 | 3.108    | 0.009   | 770.852  | -3.406   |

| Min-res arc for this Bump have    | 17                                          | ( 981.485 , 4333.41 | 5) M8  | 3.099    | 0.009   | 773.620  | -2.768   |

| 2 John ros bigger than the BJC B  | 1.8                                         | ( 979.735 , 4329.91 | 5) M8  | 3.091    | 0.008   | 783.963  | -10.342  |

| 3.2ohm res, bigger than the B2C_R | 19                                          | ( 979.360, 4326.16  | 5) M8  | 3.080    | 0.010   | 797.242  | -13.280  |

| hreshold 0.5ohm                   | Ĩ                                           |                     |        | R↑       |         | ******   | TEE      |

*The long routing from Bump to Clamp cause high resistance*  Use short path trace(SPT) utility to highlight the min-res path from the Bump to the selected clamp

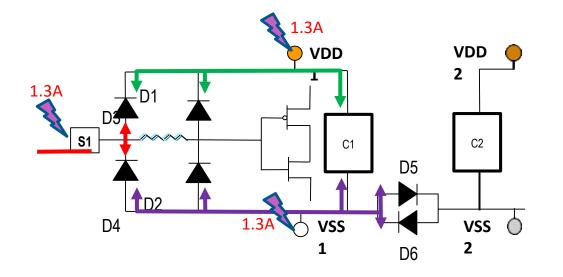

#### Rule Based CD Check

Current Density check rule : 1. Bump2Clamp check: from All pad to corresponding Clamp/Diode zap 1.3A current

14 © 2017 ANSYS, Inc. July 31, 2017

#### Analogix CD Check Case

|                                                                                                                                                                         |   |          |                                   |                                                     | - 1                           |                             |             |                                |                      |     |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-----------------------------------|-----------------------------------------------------|-------------------------------|-----------------------------|-------------|--------------------------------|----------------------|-----|-------|

|                                                                                                                                                                         |   |          |                                   |                                                     |                               | - 1                         |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          |                                   |                                                     |                               |                             |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          |                                   |                                                     |                               |                             |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          |                                   |                                                     |                               |                             |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          |                                   |                                                     |                               |                             |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          |                                   |                                                     |                               |                             |             |                                |                      |     |       |

|                                                                                                                                                                         |   |          | List                              | of Worst                                            | EM                            |                             |             |                                | _                    | _10 | (×)   |

|                                                                                                                                                                         |   | *        |                                   | Show All                                            |                               | 12                          |             |                                |                      |     | Carro |

| - Power                                                                                                                                                                 | • | ¥ [      |                                   |                                                     |                               | End Y                       | Layer       | Net                            | EM[%]                | -   | •     |

|                                                                                                                                                                         |   | ¥ [      | Red                               | Show All<br>Start Y                                 |                               |                             | Layer<br>M2 | Net<br>CLK26M_SINE_O           | EM[%]<br>188.074%    | -   | Carro |

| - Power<br>- • VDDCORE (0 of 0 >= 100%)<br>- • VDDEFU (2 of 16 >= 100%)<br>- • VNF (0 of 0 >= 100%)                                                                     |   |          | Red 🔹                             | Show All<br>Start Y<br>236 295                      | End X 2966.605                | End Y<br>236.545            | 1           |                                |                      | -   | •     |

| <ul> <li>Power</li> <li>VDDCORE (0 of 0 &gt;= 100%)</li> <li>VDDEFU (2 of 16 &gt;= 100%)</li> <li>VWF (0 of 0 &gt;= 100%)</li> <li>VWC_1 (0 of 0 &gt;= 100%)</li> </ul> |   | 22       | Red    Red    Start X  2966.605   | Show All<br>Start Y<br>236 295<br>233 255           | End X 2966.605                | End Y<br>236.545            | M2          | CLK26M_SINE_O                  | 188.074%<br>188.074% | -   | •     |

| <ul> <li>O VDDCORE (0 of 0 &gt;= 100%)</li> <li>O VDDEFU (2 of 16 &gt;= 100%)</li> <li>O VNF (0 of 0 &gt;= 100%)</li> </ul>                                             | • | 22<br>23 | Red   Start X  2966.605  2966.605 | Show All<br>Start Y<br>236 295<br>233 255<br>76 460 | End X<br>2966.605<br>2966.605 | End Y<br>236.545<br>236.295 | M2<br>M2    | CLK26M_SINE_O<br>CLK26M_SINE_O | 188 074%             | -   | •     |

X Show Net Browser

Net: AVSE\_PLL Wire: N1 [ Id = 11346086 ] Width: 0.14 un Length: 0.19 um Coordinates: (2945.79, 76.39) (2945.98, 76.39) (2945.98, 76. Resistance: 0.45 Ohm Metal Density: 0.462 Querypoint (2945.9150, 76.4530) Voltage at guery position: 0.05734324 V Current parallel to wire direction at query position: 0.0178 Half node scale: 0.9 EM mode: peak EM rule: polynomial based (length: NAX, widthLookUp; 0.126 u EM percentage: 178.32% (EM current limit: 0.00999375 A)

Max EM in this net is 188% , bigger than the threshold 100% **Bad M1 connection cause the EM violation**

#### **Performance Summary**

|                          | STAGE                                      | WALL TIME      | MEMORY USAGE(GB) |  |  |

|--------------------------|--------------------------------------------|----------------|------------------|--|--|

|                          | GDS2DB                                     | 42mins         | 49               |  |  |

| Set                      | up Design + Extraction                     | 2 hour 56 mins | 73               |  |  |

| Pasistanca               | Bump to Bump Check ( All ARCs )            |                | 79               |  |  |

| Resistance<br>Check      | Clamp to Clamp Check<br>( Diode to Clamp ) | 3hour 10 mins  |                  |  |  |

| Current Density<br>Check | Bump to Clamp Check( All ARCs )            | 2 hour 20 mins | 103              |  |  |

\*this performance are got without any reduction in design or metal geometries.

## PathFinder: Full chip ESD Integrity Sign-off

#### ESD Integrity Verification and Sign-off with PathFinder

17 © 2017 ANSYS, Inc. July 31, 2017

## 感谢聆听